# Engineered Porous Silicon Counter Electrodes for High Efficiency Dye-Sensitized Solar Cells

William R. Erwin,<sup>†</sup> Landon Oakes,<sup>‡</sup> Shahana Chatterjee,<sup>§</sup> Holly F. Zarick,<sup>†</sup> Cary L. Pint,<sup>\*,§</sup> and Rizia Bardhan<sup>\*,†</sup>

<sup>†</sup>Department of Chemical and Biomolecular Engineering, <sup>‡</sup>Interdisciplinary Materials Science Program, <sup>§</sup>Department of Mechanical Engineering, Vanderbilt University, Nashville, Tennessee 37235, United States

Supporting Information

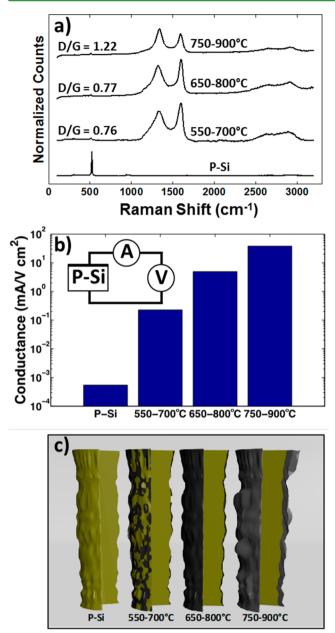

**ABSTRACT:** In this work, we demonstrate for the first time, the use of porous silicon (P-Si) as counter electrodes in dye-sensitized solar cells (DSSCs) with efficiencies (5.38%) comparable to that achieved with platinum counter electrodes (5.80%). To activate the P-Si for triiodide reduction, few layer carbon passivation is utilized to enable electrochemical stability of the silicon surface. Our results suggest porous silicon as a promising sustainable and manufacturable alternative to rare metals for electrochemical solar cells, following appropriate surface modification.

KEYWORDS: dye-sensitized solar cell, counter electrodes, porous silicon, graphene, surface passivation, solar energy conversion

## 1. INTRODUCTION

Dye-sensitized solar cells (DSSCs) have emerged as a promising third-generation solar cell due to efficiencies so far measured up to  $12\%^{1-6}$  and straightforward processes for solar cell manufacturing. A conventional DSSC functions based upon an anode interface between TiO<sub>2</sub> and dye molecules yielding dye photo-oxidation and charge transfer to an iodide/triiodide ( $I^-/I_3^-$ ) redox couple under illumination. The redox couple is regenerated using a metal counter electrode. Platinum is used as the counter electrode due to its corrosion resistance to iodide/triiodide redox couple.<sup>7–9</sup> However, evolution toward DSSCs that can be cheaply manufactured with low-cost, sustainable materials provides a key incentive toward the development and widespread commercialization of DSSCs.<sup>10</sup>

In recent years, numerous reports have demonstrated the ability to utilize alternative counter electrode materials for DSSCs with performance approaching Pt. This primarily involves the utilization of carbon nanotubes,<sup>11–13</sup> graphene,<sup>14–17</sup> hybrid carbon nanotube–graphene materials,<sup>18,19</sup> and other carbon nanostructures.<sup>20,21</sup> Whereas such approaches yield excellent promise for the use of all-carbon counter electrodes to replace Pt, cell-level integration of such materials is not aided by the high raw-materials cost of carbon nanostructures, which can often be greater than Pt (e.g., > \$100/gram), and the requirement to process such raw materials into usable architectures for electrodes that can add significant manufacturing-related costs. Other materials, such as Fe<sub>2</sub>O<sub>3</sub> and TiN nanostructures, polymer films, and Cu–Zn–Sn–S have

been demonstrated as effective counter electrodes,<sup>22–25</sup> even though challenges regarding stability, efficiency, and conduction properties can be compromised in such alternative systems.

We propose in this study, that silicon is a viable candidate for DSSC electrodes. As the manufacturing of silicon materials is central to electronics and photovoltaics industries, large-scale processing of silicon is cost-effective in comparison to other material options where expensive process development routes are necessary. Furthermore, due to its earth abundance, metallurgical grade silicon materials, which are practical for such applications due to their lower purity requirements than electronics, can be obtained at \$2-5/kg. Based purely on raw materials cost, this provides over a 1000× reduction over Pt, if silicon could be a viable electrode material. Whereas the total cost of a DSSC is based on the combined materials and manufacturing costs, silicon is a unique alternative that is promising in both of these areas. Nonetheless, silicon is a material with surface properties strongly influenced by environmental factors, and is highly reactive with ambient air and electrochemical conditions. As a result, in industrial-scale applications where silicon is employed, a critical factor enabling usability is the controlled chemical passivation of exposed silicon surfaces, an area of research which has thrived over the past few decades.<sup>26</sup> In the particular case of porous silicon (P-Si) materials produced from bulk silicon by electrochemical

Received: May 24, 2014 Accepted: June 2, 2014 Published: June 2, 2014

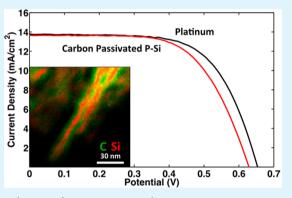

Figure 1. (a) Low resolution TEM image of carbon coated porous silicon. (b) Energy-dispersive spectroscopy map of carbon coated porous silicon with a HAADF STEM image in the inset. (c) High resolution TEM image of few layer graphene on silicon surface.

etching, such routes are especially important due to the significantly enhanced exposed surface area that could potentially provide more catalytically active sites for the  $I_3^{-/}$  I<sup>-</sup> redox reaction as a DSSC electrode.<sup>14,19</sup> A variety of routes to passivate the P-Si surface have been described, which can mostly be characterized as involving a Si–O or Si–C surface termination.<sup>27,28</sup> Whereas such routes have been utilized extensively in chemical or biological sensing,<sup>29</sup> controlled surface passivation of P-Si remains unexplored for applications in electrochemical energy conversion platforms.

In this work, we specifically utilize a thermal route to passivate P-Si materials with few-layered coatings of carbon to provide an electrochemically stable DSSC electrode that exhibits performance comparable to Pt. We emphasize the importance of complete silicon surface passivation to enable optimized device performance, and the function of a 3-D porous material to optimize the redox activity. As thermally induced carbon passivation is one of many potential surface stabilization chemistries for silicon, we emphasize silicon as a manufacturable, low-materials cost, and chemically versatile platform for scalable surface modification and replacement of rare metals conventionally employed as DSSC electrodes.

#### 2. EXPERIMENTAL SECTION

TiO<sub>2</sub> Anode Preparation. Anodes were fabricated by first drilling holes in FTO glass (MTI Corp.). FTO glass slides were then sonicated in successive baths of isopropyl alcohol/acetone with 1% Triton-X100 and isopropyl alcohol/acetone for 30 min each, respectively. Glass slides were rinsed with acetone, then isopropyl alcohol, and dried with nitrogen. Glass slides were treated with 40 mM TiCl<sub>4</sub> in water for 30 min at 70 °C and then dried in air. A 10  $\mu$ m thick layer of 20 nm TiO<sub>2</sub> nanoparticles (Dyesol Inc., MS002010) was applied via the doctor blade technique onto the FTO glass using one layer of Scotch tape (3M) to control the thickness of the layer. TiO<sub>2</sub> coated anodes were annealed at 500 °C for 30 min in air followed by another 40 mM TiCl<sub>4</sub> treatment for 12 h at 35 °C. This treatment is crucial to cell performance as a TiO2 sol gel is formed and fills gaps in the mesoporous TiO<sub>2</sub> nanoparticle layer preventing recombination of e<sup>-/</sup> h<sup>+</sup> pairs. A scattering layer composed of 300 nm TiO<sub>2</sub> nanoparticles (Dyesol Inc., MS002260) is added on top of the active layer and annealed at 500  $^\circ\text{C}.$  Finally, anodes were immersed in 0.6 mM cisbis(isothiocyanato) bis(2,2'-bipyridyl-4,4'-dicarboxylato)ruthenium-(II) (N-719 Dye) in ethanol overnight (Sigma, 703206).

**C-Passivation of Porous Silicon.** Highly boron-doped  $(0.01-0.2 \Omega \text{cm})$  silicon wafers (University Wafer) were etched in an electrochemical cell using a spiral Pt counter electrode according to our previously published procedure.<sup>30</sup> A 180 s etch process was utilized with a current density of 45 mA/cm<sup>2</sup> in a 3:8 v/v HF (50% H<sub>2</sub>O by volume) and ethanol solution. This produces porous silicon materials with  $\sim 75\%$  porosity, confirmed by optical reflectrometry, and an average pore size just under 25 nm.<sup>31</sup> Porous silicon was stored under N<sub>2</sub> until carbonization. For C-passivation, a porous silicon wafer was placed into a tube furnace at room temperature and the furnace was evacuated to 2 mTorr. Next, 1000 sccm of Ar and 200 sccm of H<sub>2</sub> were introduced to the system and the furnace was ramped to  $T_1$ .  $T_1$ was equal to 550, 650, and 750 °C for the three different C-passivated P-Si samples, respectively. The purpose of the H<sub>2</sub> is to maintain a reducing environment that preserves the surface stability of the unpassivated porous silicon from oxidation. Acetylene was introduced and the temperature was ramped to  $T_1$  + 100. Ten minutes after  $C_2H_2$ introduction, the temperature was ramped to  $T_1$  + 150 for 10 min. This process was chosen because our observations in preliminary experiments demonstrated (i) porous silicon is not thermally stable without passivation above 750 °C, (ii) carbon coating thermally stabilizes the porous silicon up to ~1000 °C or higher, and (iii) the best "quality" of carbon materials based on Raman spectroscopy analysis were formed in the temperature range between 550 and 850 °C. Therefore, these conditions are able to optimize both the reactivity of the silicon for coating, the quality of carbon material, and the preservation of the nanoscale structure of the porous silicon after treatment. Following the second 10 min step, C2H2 flow was discontinued and the sample was allowed to cool to 50 °C in an Ar and H<sub>2</sub> atmosphere. Samples were stored in an N<sub>2</sub> atmosphere until use to prevent oxidation.

**DSSC Fabrication.** Platinum cathodes were prepared by brushing 25 mM  $H_2PtCl_6$  (Sigma 254029) in isopropyl alcohol onto clean FTO glass substrates. Samples were then calcined at 450 °C for 1 h. The cathode and anode were heat sealed with Surlyn film (McMaster Carr, 7622A41) and filled with the electrolyte composed of 50 mM  $I_2$ , 500 mM LiI, and 500 mM tertbuylpyridine (TBP) in acetonitrile, and heat sealed.

**Electrochemical Testing.** Dye-sensitized solar cells were tested over a potential range of -1 to +1 V at a scan rate of 50 mV/s under AM 1.5 illumination (100 mW/cm<sup>2</sup>) with a Newport solar simulator and power supply. An area of 0.12 cm<sup>2</sup> was illuminated; the remainder was covered with a shadow mask. Cyclic voltammetry (CV) measurements were carried out in a three-electrode setup using nitrogen bubbled acetonitrile which contained 0.1 M LiClO<sub>4</sub>, 10 mM LiI, and 1 mM I<sub>2</sub> as an electrolyte over a potential range of +1 to -0.8 V. A Pt foil was used as the counter electrode, and Ag/AgCl was used as a reference electrode. Electrochemical impedance spectroscopy measurements were performed over a frequency range of  $10^{-1}$  to  $10^{5}$  Hz. A MetroOhm PGSTAT101 potentiostat was used for all electrochemical measurements.

**Material Characterization.** An FEI Osiris transmission electron microscope was used with an accelerating voltage of 200 kV for all transmission electron microscopy (TEM) imaging. Raman spectra were gathered using a 532 nm DPSS laser in which the output power was limited to 10% (maximum output power 50 mW). The Raman

scattered photons were dispersed by a 1200 lines/mm grating monochromator and collected by a CCD camera with a 50 $\times$  objective lens.

## 3. RESULTS AND DISCUSSION

Thermal passivation of P-Si materials was achieved, consistent with our previous studies,<sup>30</sup> and building from efforts by Salonen et al.<sup>32,33</sup> This involves exposure of P-Si to an environment containing a diluted  $C_2H_2$  active species (<0.1%) in H<sub>2</sub>/Ar. To achieve full passivation and maintain structural integrity of the P-Si nanoscale features, we observed the passivation temperature to be important. Prolonged exposure to temperatures greater than 750 °C led to irreversible structural changes to the P-Si, which were alleviated by introducing temperature ramps from below 750 °C to temperatures above this, as the formation of a thin carbon coating passivated the surface from thermal degradation at high temperatures. As discussed at a later point, our most ideal temperature ramp condition was obtained between 650 and 800 °C, which enabled complete catalytic surface passivation without thermal decomposition of the C2H2 species that was found to yield low-quality carbon materials. Whereas we chose thermal passivation for our work, progress in silicon surface passivation using wet chemical approaches, such as surface alkylation,<sup>34,35</sup> could ultimately enable a similar outcome to the results we discuss here.

The morphology of the carbon coated porous silicon is shown via low resolution TEM (Figure 1a). To confirm and assess the presence of carbon on the silicon surface after thermal passivation, a high angle annular dark field (HAADF) image was obtained with energy-dispersive X-ray spectroscopy (EDS) mapping of carbon and silicon (Figure 1b); the corresponding spectrum is in the Supporting Information (Figure S1). A high resolution TEM image showing the carbon-silicon interface and presence of few-layer carbon coatings is presented in Figure 1c. To assess the carbon material properties, fast Fourier transform analysis was used to determine the interlayer spacing, which was found to be between 0.35 and 0.37 nm (Supporting Information, Figure S2). This spacing represents a graphene material with interlayer defects; it is greater than pristine defect-free graphene (~0.34 nm)<sup>36,37</sup> but lower than most forms of chemically processed graphene, such as reduced graphene oxide (often >0.4 nm).<sup>38</sup> Therefore, we emphasize under these conditions, that the thermal surface passivation of P-Si leads to a uniform, fewnanometer thick coating of conformal graphene layers catalyzed by the nanoscale silicon material.

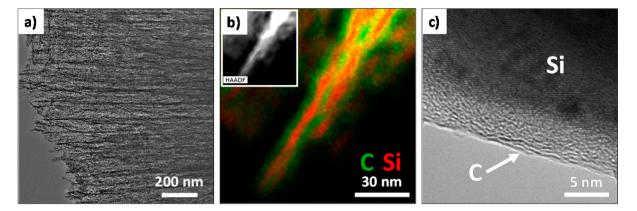

DSSCs with C-passivated porous silicon counter electrodes were designed by depositing a TiO<sub>2</sub> active layer adsorbed with Di-tetrabutylammonium *cis*-bis(isothiocyanato)bis(2,2'-bipyridyl-4,4'-dicarboxylato)ruthenium(II) (N719) dye on the fluorine tin oxide (FTO) glass followed by a TiO<sub>2</sub> scattering layer. A liquid electrolyte consisting of the  $I^-/I_3^-$  redox couple was utilized for electron transport between the electrodes. A schematic representation of a typical DSSC made with Cpassivated porous silicon is illustrated in Figure 2a and the front and back views of the counter electrode are shown in Figure 2b.

The characteristics of the P-Si surface passivation are observed to directly correlate with DSSC performance. To study the effect of C-passivation on the catalytic properties of porous silicon, DSSCs were fabricated with pristine P-Si and thermal passivation at three different temperature ramp profiles including 550-700, 650-800, and 750-900 °C (details in the

Research Article

**Figure 2.** (a) Schematic of dye-sensitized solar cells fabricated with C-passivated porous silicon counter electrode. (b) Front (left) and back (right) view of DSSC with C-passivated porous silicon counter electrode.

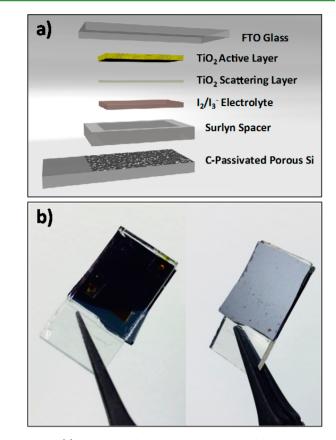

Experimental Section). The C-passivation layer was characterized by acquiring Raman spectra for all four samples (Figure 3a). Pristine P-Si has a single strong peak near 520  $\text{cm}^{-1}$ , indicative of silicon. After thermal passivation, two distinctive peaks arise at 1325 cm<sup>-1</sup> (D-band) and 1602 cm<sup>-1</sup> (G-band) that are characteristic of graphitic carbon coatings.  $^{39}$  The D/Gpeak height is indicative of the ratio of sp<sup>3</sup> to sp<sup>2</sup> hybridized carbon species, which is notably consistent at D:G = 0.76 until the highest temperature conditions (750-900 °C), where D:G is 1.22. We attribute this to a decrease in crystallinity of the Cpassivation layer associated with higher temperature noncatalytic decomposition of C<sub>2</sub>H<sub>2</sub> species. Notably, we do not observe the presence of a significant oxide layer on the silicon, which is evident in the Raman spectra through a bump near 800 cm<sup>-1</sup>. To better understand the properties of C-passivation, we measured conductance through the P-Si layer in the different C-passivated P-Si materials. It is known that P-Si materials exhibit defect-induced surface traps that can reverse the effect of chemical doping and decrease the P-Si conductance by several orders of magnitude.<sup>40</sup> Measurements were carried out by sandwiching porous silicon electrodes between two plates connected with copper wires, and performing I-V curves (Supporting Information). This forces the porous silicon layer to be a resistive component in series with the bulk silicon, enabling us to assess the effect of surface passivation on the porous silicon electrical properties. We find the conductance to increase between 3 and 5 orders of magnitude through C-passivation, calculated over the ohmic region from current-voltage scans shown in Figure 3b. This

**Figure 3.** (a) Raman spectra of pristine porous silicon and porous silicon C-passivated at different temperatures, peaks are normalized to the 1602 cm<sup>-1</sup> G-peak. (b) Calculated conductance values for porous silicon and C-passivated porous silicon at different temperatures with (inset) schematic of through plane measurement setup. (c) Schematic representation of carbon coating (black) on a section of porous silicon (yellow) for each sample type. The coating coverage and thickness were determined using data from cyclic voltammetry, electrochemical impedance spectroscopy, and through plane conductivity. The structure on the right is shaded differently to indicate the higher ratio of sp<sup>3</sup> to sp<sup>2</sup> carbon.

observation is complemented by two additional observations: (i) post C-passivation Si etch experiments in KOH led to small, polydispersed flakes at 550-700 °C and coherent films at 650-800 °C (Supporting Information, Figure S4) and (ii) TEM imaging of C-passivated regions did not show a distinct layer thickness dependence between the different C-passivation temperatures. We do not anticipate that the formation of an oxide layer would affect this result because we observe no presence of an oxide layer in these materials (Raman and TEM analysis), and any effect of an oxide layer on the conductivity would be consistent across all samples. This leads us to conclude that (i) ramp conditions with terminal temperatures below 700  $^{\circ}$ C lead to incomplete surface passivation, in turn leading to exposed Si surface, (ii) ramp conditions from 650 to 800  $^{\circ}$ C lead to ideal surface passivation, and (iii) terminal temperatures in ramp conditions of 900  $^{\circ}$ C and above lead to thicker, less crystalline carbon passivation layers (Figure 3c).

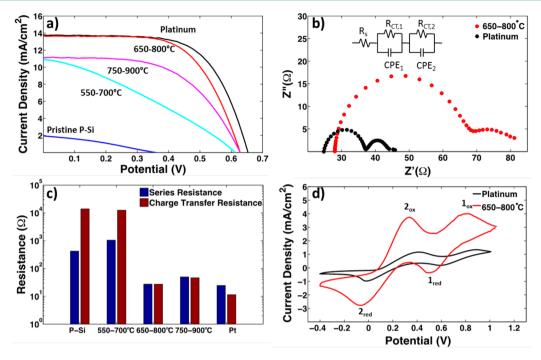

DSSCs were constructed with the C-passivated porous silicon fabricated at the three conditions and compared to reference DSSCs constructed with standard Pt counter electrodes. Photocurrent spectra of DSSCs under AM 1.5 illumination are shown in Figure 4a. The short circuit current density  $(I_{sc})$ , open circuit voltage  $(V_{oc})$ , calculated efficiency, and fill factor (FF) are summarized in Table 1. DSSCs with a P-Si counter electrode exhibited an efficiency of 0.21% relative to an efficiency of 5.80% for the platinized FTO counter electrodes, which we can attribute to either the poor electrochemical stability native to unpassivated silicon that drives corrosion, the lack of conductivity (Figure 3b), or the lack of catalytically active sites for triiodide reduction that are developed through surface modification. DSSCs made with 650-800 °C C-passivated P-Si exhibited an efficiency of 5.38%, which is comparable to that of solar cells constructed using Pt counter electrodes. Comparatively, DSSCs constructed with Cpassivation conditions of 550-700 °C and 750-900 °C exhibited efficiencies of 2.13% and 3.95%, respectively. This indicates C-passivation at temperatures of 650-800 °C leads to ideal performance that seems to correlate with previous material charge-transport analysis shown in Figure 3. We also note that DSSCs fabricated with C-passivation at 750-900 °C had a relatively good efficiency and fill factor compared to P-Si and those constructed at 550–700  $^{\circ}\text{C}.$  This can be attributed to the full coverage and passivation of porous silicon by carbon which minimizes the charge recombination on the surface and lowers the charge transfer resistance. Long-term illumination studies of the passivated P-Si counter electrodes in comparison to Pt (Supporting Information, Figure S7) emphasize the ability for the passivation layer to enable long-term operation of this electrode material.

To understand these inherent differences in performance, the C-passivated P-Si counter electrodes were characterized with electrochemical impedance spectroscopy (EIS), and cyclic voltammetry. EIS was performed on symmetric counter electrode cells over a frequency range of  $10^{-1}$  to  $10^{5}$  Hz in order to investigate the charge transfer properties in the system (Figure 4b). The first semicircle is representative of the charge transfer resistance and double layer capacitance at the cathode. The second, low frequency semicircle is indicative of electrolyte diffusion between electrodes. The observed differences in the impedance between the DSSCs constructed with the Pt counter electrode and the C-passivated P-Si at 650–800 °C (Figure 4b) are attributed to a combination of (i) higher resistance to electron transfer, stemming from the insulating porous silicon interface between the carbon coating and conductive silicon substrate and (ii) slower ionic diffusion, likely due to the poor reduction of triiodide species at the C-passivated P-Si relative to the planar Pt. To further elucidate these mechanisms, an appropriate equivalent circuit model was fit to the system<sup>41</sup> provided in the inset of Figure 4b. Series  $(R_s)$  and charge transfer  $(R_{ct})$  resistances were calculated from the circuit model shown in Figure 4c. The model reveals that the series and charge transfer resistances of both pristine P-Si and C-

**Figure 4.** (a) J–V curves of DSSCs designed with the C-passivated porous silicon fabricated at different temperatures under AM 1.5 G illumination. The J–V curve of the Pt counter electrode is included as well. (b) Nyquist plots of symmetric cells made from carbon coated porous silicon and platinum under zero voltage bias over a frequency range of  $10^{-1}$  to  $10^5$  Hz with equivalent circuit diagram provided (inset). Here CPE refers to constant phase element,  $R_{ct}$  refers to charge transfer resistance, and  $R_s$  refers to series resistance. (c) Calculated series and charge transfer resistances of different counter electrodes measured over identical P–Si sample areas of 0.12 cm<sup>2</sup>. (d) Cyclic voltammograms of carbon coated porous silicon fabricated at 650–800 °C and Pt. Reaction 1 refers to  $3I_2 + 2e^- \rightarrow 2I_3^-$  and reaction 2 refers to  $I_3^- + 2e^- \rightarrow 3I^-$ , the latter occurring at the counter electrode.

Table 1. Efficiencies, Fill Factors, Short Circuit Currents andOpen Circuit Voltages of All Devices

| counter electrode | efficiency (%) | FF (%) | $J_{\rm sc}~({\rm mA/cm^2})$ | $V_{\rm oc}$ (V) |

|-------------------|----------------|--------|------------------------------|------------------|

| P-Si              | 0.21           | 31.5   | 1.94                         | -0.36            |

| 550-700 °C        | 2.13           | 31.8   | 10.9                         | -0.61            |

| 650-800 °C        | 5.38           | 62.4   | 13.7                         | -0.63            |

| 750-900 °C        | 3.85           | 56.6   | 11.1                         | -0.63            |

| Pt                | 5.80           | 64.4   | 13.8                         | -0.65            |

passivated P-Si thermally treated at 550-700 °C are orders of magnitude higher than the corresponding resistances of samples treated at 650-800, 750-900 °C, and Pt. The magnitude of the resistances found with P-Si and the 550-700 °C sample is attributed to corrosion occurring on exposed Si surface.<sup>34,35</sup> Series resistance varies with C-passivation thickness,<sup>38,39</sup> and is lowest for the platinum sample, increases for the 650-800 °C sample and 750-900 °C sample.<sup>42,43</sup> It should be noted that this is qualitatively in agreement with throughplane conductivity measurements (Figure 3b), even though this value of  $R_s$  is more relevant to the electrode-limited resistance of the full device with the porous silicon-electrolyte interface. The lower R<sub>ct</sub> of Pt is a result of less recombination at the cathode relative to C-passivated P-Si, and hence slightly faster kinetics of triiodide reduction that is indicative of an efficient counter electrode material. The 750-900 °C treated P-Si sample has a higher  $R_{ct}$  than the 650–800 °C treated samples due to its reduced ability for triiodide reduction, a result of its highly defective carbon coating. These effects enhance the interfacial charge transfer events, lower the overall resistance, and augment the efficiencies and fill factor. For the sake of clarity, Nyquist plots of only Pt counter electrodes and C-

passivated P-Si thermally treated at 650–800 °C are shown in Figure 4b; Nyquist plots for other counter electrodes are provided in the Supporting Information (Figure S5).

To further understand the electrochemical properties of the different C-passivated porous silicon samples, cyclic voltammetry (CV) measurements were carried out in a three-electrode setup, as detailed in the Supporting Information. The CV curve of the Pt counter electrode (Figure 4d) is similar to that found in the literature.<sup>44</sup> Two sets of peaks were observed, corresponding to the reduction of iodine to triiodide given by redox reactions 1 and reduction of triiodide to iodide ions given by reaction 2

$$3I_2 + 2e^- \rightarrow 2I_3^- \tag{1}$$

$$I_3^- + 2e^- \to 3I^- \tag{2}$$

The separation of the reduction and oxidation peaks,  $E_{pp}$ , is indicative of the electrochemical catalytic activity of the counter electrodes, which is independent of their surface area.<sup>14,45</sup> Values for  $E_{pp}$  of 0.40 and 0.43 V were found for the samples passivated at 650–800 °C and Pt, respectively, which indicates that the catalytic ability of C-passivated P-Si for the  $I^-/I_3^$ redox couple is on par with Pt. Porous-Si samples passivated at 750–900 °C exhibited an  $E_{pp}$  value of 0.54, indicating that the surface passivation at the higher temperatures is not as effective of a catalyst, due to the high defect ratio.<sup>46</sup> Due to the high surface area of porous silicon, the redox peaks are much larger for the C-passivated P-Si than for the planar Pt, which explains the comparable efficiencies of the DSSCs. CV measurements of both P-Si and the C-passivated samples at 550–700 °C (Supporting Information, Figure S6) show their poor catalytic activity for  $I^-/I_3^-$  oxidation reaction. The incomplete

passivation achieved at 550-700 °C likely gives rise to high charge recombination on the exposed Si and inadequate redox chemistries resulting in low efficiency and poor fill factor. We note that we also performed a control experiment using planar silicon as a counter electrode for DSSC (Supporting Information, Figure S7) and did not observe a measurable

photocurrent. Overall, whereas we emphasize in this work that passivated Si materials are viable candidates for the replacement of Pt in DSSCs, our results indicate a synergistic codependence of the passivation layer and silicon material properties that dictates overall behavior. In regimes of incomplete passivation, poor device performance is indicative of poor charge-transport properties and a high R<sub>ct</sub> that inhibits redox activity. However, in regimes of complete passivation with poor quality coatings, inefficient redox activity inhibits performance matching that of Pt reference cells. The benefit of silicon in such a material platform is the tunable surface chemistry between the silicon and carbon that can enable optimal performance as a counter electrode in a DSSC. Whereas we demonstrate this to be a viable platform that can be utilized in the context of an on-chip system, we emphasize the versatility of this technique's scale to a diverse scope of microscale and nanoscale silicon heterogeneous materials that can provide a new, sustainable alternative material for efficient DSSC fabrication. In comparison to other solar energy conversion systems using silicon, where processing and interface optimization are necessary to enable efficient device performance, we demonstrate heterogeneous porous silicon materials that natively exhibit the capability to be electrodes for DSSCs with appropriate surface modification.

## 4. CONCLUSIONS

Although our specific work is focused on thermally applied carbon passivation layers resembling graphene, the use of silicon reflects a versatile chemical platform for optimizing the electrode-electrolyte interface in a DSSC using scalable routes such as wet-chemical, thermal, and electrochemical passivation. Compared to other homogeneous materials employed as counter electrodes in DSSCs, this approach represents the utilization of a heterogeneous material interface that we propose provides enhanced flexibility in achieving scalable device optimization. As silicon exists in nearly all applications as a heterogeneous material in some form, and these applications represent the majority of our current technological infrastructure, we see this approach as directly building upon a material platform already integrated into scalable industrial manufacturing processes. Furthermore, as DSSCs involve a native low-cost cell design with promise for versatility and cost that could ultimately replace silicon photovoltaics, we emphasize the fascinating notion of silicon to empower such a transition for DSSCs. As raw material costs of silicon are only a minor portion of commercial PV costs, the low-cost assembly of Si-based DSSCs to replace conventional PV platforms could build upon, instead of compete with, aggressive worldwide government-corporate investments aimed to improve silicon manufacturing for solar applications.

#### ASSOCIATED CONTENT

#### **S** Supporting Information

EDS spectrum corresponding to Figure 1b, TEM and FFT of graphene oxide with d-spacing of 0.35-0.36 nm, through plane conductivity measurements over the potential range of -100mV to +100mV for each porous silicon sample used,

through plane conductivity schematic, image of the carbon coating when silicon has been dissolved away via KOH etching, Nyquist plots and corresponding modeled data for symmetric cells, cyclic voltammograms of all samples carried out in a three-electrode setup using nitrogen bubbled acetonitrile, and stability tests of DSSCs with Pt and C-passivated P-Si counter electrodes over 2 h. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

#### **Corresponding Authors**

\*R.B. E-mail: rizia.bardhan@vanderbilt.edu.

\*C.L.P. E-mail: cary.l.pint@vanderbilt.edu.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

We thank S. Weiss for use of facilities utilized in part for P-Si fabrication. This work was supported by (W.R.E., H.F.Z., and R.B.) NSF EPSCOR (EPS 1004083) and NSF BRIGE (EEC 1342185), and C.L.P. and L.O. were supported by NSF CMMI 1334269. TEM images were obtained with an instrument supported by NSF EPS 1004083. Imaging and CVD materials fabrication parts of this research were in part conducted at the Center for Nanophase Materials Sciences, which is sponsored at Oak Ridge National Laboratory by the Scientific User Facilities Division, Office of Basic Energy Sciences, U.S. Department of Energy.

#### REFERENCES

(1) Yella, A.; Lee, H.-W.; Tsao, H. N.; Yi, C.; Chandiran, A. K.; Nazeeruddin, M. K.; Diau, E. W.-G.; Yeh, C.-Y.; Zakeeruddin, S. M.; Grätzel, M. Porphyrin-Sensitized Solar Cells with Cobalt (II/III)-Based Redox Electrolyte Exceed 12 Percent Efficiency. *Science* **2011**, *334*, 629–634.

(2) Chandiran, A. K.; Tetreault, N.; Humphry-Baker, R.; Kessler, F.; Baranoff, E.; Chenyi; Nazeeruddin, M. K.; Grätzel, M. Subnanometer Ga<sub>2</sub>O<sub>3</sub> Tunnelling Layer by Atomic Layer Deposition to Achieve 1.1 V Open-Circuit Potential in Dye-Sensitized Solar Cells. *Nano Lett.* **2012**, *12*, 3941–3947.

(3) Tétreault, N.; Arsenault, É.; Heiniger, L.-P.; Soheilnia, N.; Brillet, J.; Moehl, T.; Zakeeruddin, S.; Ozin, G. A.; Grätzel, M. High-Efficiency Dye-Sensitized Solar Cell with Three-Dimensional Photoanode. *Nano Lett.* **2011**, *11*, 4579–4584.

(4) Chen, T.; Qiu, L.; Cai, Z.; Gong, F.; Yang, Z.; Wang, Z.; Peng, H. Intertwined Aligned Carbon Nanotube Fiber Based Dye-Sensitized Solar Cells. *Nano Lett.* **2012**, *12*, 2568–2572.

(5) Kavan, L.; Yum, J.-H.; Grätzel, M. Graphene Nanoplatelets Outperforming Platinum as the Electrocatalyst in Co-Bipyridine-Mediated Dye-Sensitized Solar Cells. *Nano Lett.* **2011**, *11*, 5501–5506. (6) Green, M. A.; Emery, K.; Hishikawa, Y.; Warta, W.; Dunlop, E. D. Solar Cell Efficiency Tables (version 42). *Prog. Photovolt. Res. Appl.* **2013**, *21*, 827–837.

(7) Bonnemann, H.; Khelashvili, G.; Behrens, S.; Hinsch, A.; Skupien, K.; Dinjus, E. Role of the Platinum Nanoclusters in the Iodide/Triiodide Redox System of Dye Solar Cells. *J. Cluster Sci.* 2007, *18*, 141–155.

(8) Hauch, A.; Georg, A. Diffusion in the Electrolyte and Charge-Transfer Reaction at the Platinum Electrode in Dye-Sensitized Solar Cells. *Electrochim. Acta* **2001**, *46*, 3457–3466.

(9) Papageorgiou, N.; Maier, W. F.; Gratzel, M. An Iodine/Triiodide Reduction Electrocatalyst for Aqueous and Organic Media. J. Electrochem. Soc. **1997**, 144, 876–884.

(10) Baxter, J. B. Commercialization of Dye Sensitized Solar Cells: Present Status and Future Research Needs to Improve Efficiency, Stability, and Manufacturing. *J. Vac. Sci. Technol.*, A **2012**, *30*, 020801.

(11) Dong, P.; Pint, C. L.; Hainey, M.; Mirri, F.; Zhan, Y.; Zhang, J.; Pasquali, M.; Hauge, R. H.; Verduzco, R.; Jiang, M.; Lin, H.; Lou, J. Vertically Aligned Single-Walled Carbon Nanotubes as Low-Cost and High Electrocatalytic Counter Electrode for Dye-Sensitized Solar Cells. ACS Appl. Mater. Interfaces **2011**, *3*, 3157–3161.

(12) Nam, J. G.; Park, Y. J.; Kim, B. S.; Lee, J. S. Enhancement of the Efficiency of Dye-Sensitized Solar Cell by Utilizing Carbon Nanotube Counter Electrode. *Scr. Mater.* **2010**, *62*, 148–150.

(13) Lee, W. J.; Ramasamy, E.; Lee, D. Y.; Song, J. S. Efficient Dye-Sensitized Cells with Catalytic Multiwall Carbon Nanotube Counter Electrodes. *ACS Appl. Mater. Interfaces* **2009**, *1*, 1145–1149.

(14) Roy-mayhew, J. D.; Bozym, D. J.; Punckt, C.; Aksay, I. A. Functionalized Graphene as a Catalytic Solar Cells. *ACS Nano* **2010**, *4*, 6203–6211.

(15) Xue, Y.; Liu, J.; Chen, H.; Wang, R.; Li, D.; Qu, J.; Dai, L. Nitrogen-Doped Graphene Foams as Metal-Free Counter Electrodes in High-Performance Dye-Sensitized Solar Cells. *Angew. Chem., Int. Ed.* **2012**, *51*, 12124–12127.

(16) Kavan, L.; Yum, J. H.; Gratzel, M. Optically Transparent Cathode for Dye- Nanoplatelets. *ACS Nano* **2011**, *5*, 165–172.

(17) Zhang, D. W.; Li, X. D.; Li, H. B.; Chen, S.; Sun, Z.; Yin, X. J.; Huang, S. M. Graphene-Based Counter Electrode for Dye-Sensitized Solar Cells. *Carbon* **2011**, *49*, 5382–5388.

(18) Ma, J.; Zhou, L.; Li, C.; Yang, J.; Meng, T.; Zhou, H.; Yang, M.; Yu, F.; Chen, J. Surfactant-Free Synthesis of Graphene-Functionalized Carbon Nanotube Film as a Catalytic Counter Electrode in Dye-Sensitized Solar Cells. *J. Power Sources* **2014**, *247*, 999–1004.

(19) Velten, J.; Mozer, A. J.; Li, D.; Officer, D.; Wallace, G.; Baughman, R.; Zakhidov, A. Carbon Nanotube/Graphene Nanocomposite as Efficient Counter Electrodes in Dye-Sensitized Solar Cells. *Nanotechnology* **2012**, *23*, 085201.

(20) Peng, T.; Sun, W.; Sun, X.; Huang, N.; Liu, Y.; Bu, C.; Guo, S.; Zhao, X.-Z. Direct Tri-Constituent Co-assembly of Highly Ordered Mesoporous Carbon Counter Electrode for Dye-Sensitized Solar Cells. *Nanoscale* **2013**, *5*, 337–341.

(21) Murakami, T. N.; Ito, S.; Wang, Q.; Nazeeruddin, M. K.; Bessho, T.; Cesar, I.; Liska, P.; Humphry-Baker, R.; Comte, P.; Péchy, P. t.; Grätzel, M. Highly Efficient Dye-Sensitized Solar Cells Based on Carbon Black Counter Electrodes. *J. Electrochem. Soc.* **2006**, *153*, A2255–A2261.

(22) Hou, Y.; Wang, D.; Yang, X. H.; Fang, W. Q.; Zhang, B.; Wang, H. F.; Lu, G. Z.; Hu, P.; Zhao, H. J.; Yang, H. G. Rational Screening Low-Cost Counter Electrodes for Dye-Sensitized Solar Cells. *Nat. Commun.* **2013**, *4*, 1583.

(23) Jiang, Q. W.; Li, G. R.; Gao, X. P. Highly Ordered TiN Nanotube Arrays as Counter Electrodes for Dye-Sensitized Solar Cells. *Chem. Commun.* **2009**, 6720–6722.

(24) Xin, X. K.; He, M.; Han, W.; Jung, J. H.; Lin, Z. Q. Low-Cost Copper Zinc Tin Sulfide Counter Electrodes for High-Efficiency Dye-Sensitized Solar Cells. *Angew. Chem., Int. Ed.* **2011**, *50*, 11739–11742.

(25) Lee, K. M.; Chen, P. Y.; Hsu, C. Y.; Huang, J. H.; Ho, W. H.; Chen, H. C.; Ho, K. C. A High-Performance Counter Electrode Based on Poly(3,4-alkylenedioxythiophene) for Dye-Sensitized Solar Cells. *J. Power Sources* **2009**, *188*, 313–318.

(26) Waltenburg, H. N.; Yates, J. T. Surface-Chemistry of Silicon. Chem. Rev. 1995, 95, 1589–1673.

(27) Anderson, R. C.; Muller, R. S.; Tobias, C. W. Chemical Surface Modification of Porous Silicon. *J. Electrochem. Soc.* **1993**, *140*, 1393– 1396.

(28) Song, J. H.; Sailor, M. J. Chemical Modification of Crystalline Porous Silicon Surfaces. *Comments Inorg. Chem.* **1999**, *21*, 69–84.

(29) Chan, S.; Li, Y.; Rothberg, L. J.; Miller, B. L.; Fauchet, P. M. Nanoscale Silicon Microcavities for Biosensing. *Mater. Sci. Eng.*, C 2001, 15, 277–282.

(30) Oakes, L.; Westover, A.; Mares, J. W.; Chatterjee, S.; Erwin, W. R.; Bardhan, R.; Weiss, S. M.; Pint, C. L. Surface Engineered Porous Silicon for Stable, High Performance Electrochemical Supercapacitors. *Sci. Rep.* **2013**, *3*, 3020.

(31) Gaur, G.; Koktysh, D. S.; Weiss, S. M. Immobilization of Quantum Dots in Nanostructured Porous Silicon Films: Characterizations and Signal Amplification for Dual-Mode Optical Biosensing. *Adv. Funct. Mater.* **2013**, *23*, 3604–3614.

(32) Salonen, J.; Lehto, V. P.; Björkqvist, M.; Laine, E.; Niinistö, L. Studies of Thermally-Carbonized Porous Silicon Surfaces. *Phys. Status Solidi A* **2000**, *182*, 123–126.

(33) Salonen, J.; Laine, E.; Niinistö, L. Thermal Carbonization of Porous Silicon Surface by Acetylene. J. Appl. Phys. 2002, 91, 456.

(34) Praisai, D. T.; Tuberquia, J. C.; Harl, R. R.; Jennings, G. K.; Bolotin, K. I. Graphene: Corrosion-Inhibiting Coating. *ACS Nano* **2012**, *6*, 1102–1108.

(35) Singh Raman, R. K.; Chakraborty Banerjee, P.; Lobo, D. E.; Gullapalli, H.; Sumandasa, M.; Kumar, A.; Choudhary, L.; Tkacz, R.; Ajayan, P. M.; Majumder, M. Protecting Copper from Electrochemical Degradation by Graphene Coating. *Carbon* **2012**, *50*, 4040–4045.

(36) Reina, A.; Jia, X.; Ho, J.; Nezich, D.; Son, H.; Bulovic, V.; Dresselhaus, M. S.; Kong, J. Large Area, Few-Layer Graphene Films on Arbitrary Substrates by Chemical Vapor Deposition. *Nano Lett.* **2008**, *9*, 30–35.

(37) Lee, C.; Wei, X.; Kysar, J. W.; Hone, J. Measurement of the Elastic Properties and Intrinsic Strength of Monolayer Graphene. *Science* **2008**, *321*, 385–388.

(38) Moon, I. K.; Lee, J.; Ruoff, R. S.; Lee, H. Reduced Graphene Oxide by Chemical Graphitization. *Nat. Commun.* **2010**, *1*, 73.

(39) Ferrari, a. C.; Meyer, J. C.; Scardaci, V.; Casiraghi, C.; Lazzeri, M.; Mauri, F.; Piscanec, S.; Jiang, D.; Novoselov, K. S.; Roth, S.; Geim, a. K. Raman Spectrum of Graphene and Graphene Layers. *Phys. Rev. Lett.* **2006**, *97*, 187401.

(40) Lehmann, V.; Hofmann, F.; Möller, F.; Grüning, U. Resistivity of Porous Silicon: A Surface Effect. *Thin Solid Films* **1995**, *255*, 20–22. (41) Liberatore, M.; Decker, F.; Burtone, L.; Zardetto, V.; Brown, T.

M.; Reale, A.; Di Carlo, A. Using EIS for Diagnosis of Dye-Sensitized Solar Cells Performance. J. Appl. Electrochem. 2009, 39, 2291–2295.

(42) Imoto, K.; Takahashi, K.; Yamaguchi, T.; Komura, T.; Nakamura, J.-i.; Murata, K. High-Performance Carbon Counter Electrode for Dye-Sensitized Solar Cells. *Sol. Energy Mater. Sol. Cells* **2003**, *79*, 459–469.

(43) Joshi, P.; Xie, Y.; Ropp, M.; Galipeau, D.; Bailey, S.; Qiao, Q. Dye-Sensitized Solar Cells Based on Low Cost Nanoscale Carbon/ TiO<sub>2</sub> Composite Counter Electrode. *Energy Environ. Sci.* **2009**, *2*, 426–429.

(44) Wu, M.; Lin, X.; Wang, T.; Qiu, J.; Ma, T. Low-Cost Dye-Sensitized Solar Cell Based on Nine Kinds of Carbon Counter Electrodes. *Energy Environ. Sci.* **2011**, *4*, 2308–2315.

(45) Compton, R. G.; Banks, C. E. Understanding Voltammetry; World Scientific: Singapore, 2007.

(46) Punckt, C.; Pope, M. A.; Liu, J.; Lin, Y.; Aksay, I. A. Electrochemical Performance of Graphene as Effected by Electrode Porosity and Graphene Functionalization. *Electroanalysis* **2010**, *22*, 2834–2841.